## 5-A H-Bridge for DC-Motor Applications

#### TLE 5206-2

#### 1 Overview

#### 1.1 Features

- Delivers up to 5 A continuous 6 A peak current

- Optimized for DC motor management applications

- Operates at supply voltages up to 40 V

- Very low  $R_{\rm DS\,ON}$ ; typ. 200 m $\Omega$  @ 25 °C per switch

- Output full short circuit protected

- Overtemperature protection with hysteresis and diagnosis

- Short circuit diagnosis with open drain error flag

- Undervoltage lockout

- CMOS/TTL compatible inputs with hysteresis

- No crossover current

- Internal freewheeling diodes

- Wide temperature range;  $-40 \, ^{\circ}\text{C} < T_{\text{i}} < 150 \, ^{\circ}\text{C}$

| Туре         | Ordering Code | Package      |

|--------------|---------------|--------------|

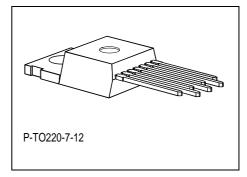

| TLE 5206-2   | Q67000-A9290  | P-TO220-7-11 |

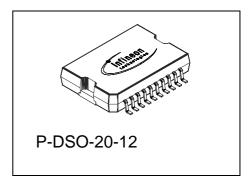

| TLE 5206-2GP | Q67006-A9239  | P-DSO-20-12  |

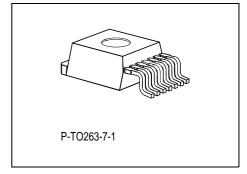

| TLE 5206-2G  | Q67006-A9323  | P-TO263-7-1  |

| TLE 5206-2S  | Q67000-A9326  | P-TO220-7-12 |

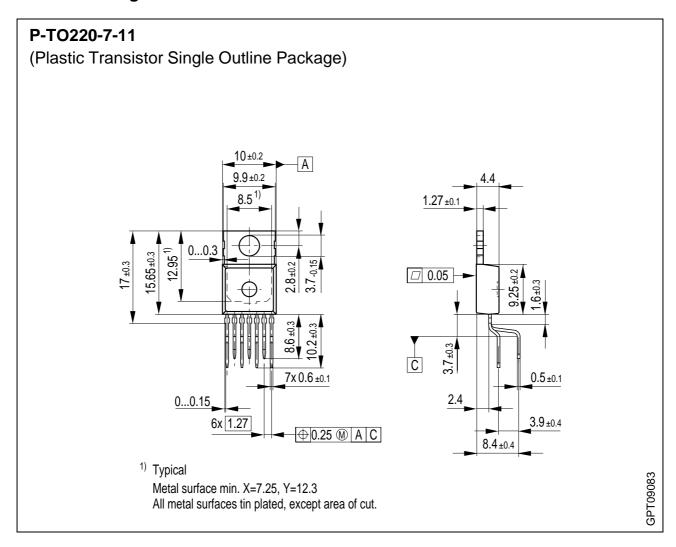

# P-TO220-7-11

# **Description**

The TLE 5206-2 is an integrated power H-bridge with DMOS output stages for driving DC-Motors. The part is built using the SIEMENS multi-technology process SPT® which allows bipolar and CMOS control circuitry plus DMOS power devices to exist on the same monolithic structure.

Operation modes forward (cw), reverse (ccw), brake

high and brake low are invoked from just two control pins with TTL/CMOS compatible levels. The combination of an extremely low  $R_{\rm DS\,ON}$  and the use of a power IC package with low thermal resistance and high thermal capacity helps to minimize system power dissipation. A blocking capacitor at the supply voltage is the only external circuitry due to the integrated freewheeling diodes.

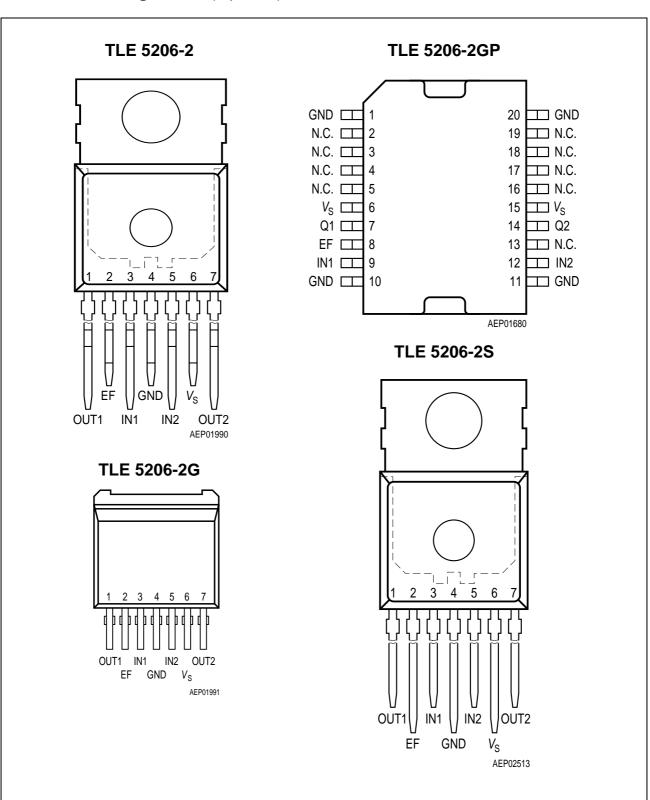

# **1.2 Pin Configuration** (top view)

Figure 1

# 1.3 Pin Definitions and Functions

| Pin No.<br>P-TO220 | Pin No.<br>P-DSO                 | Symbol  | Function                                                                                          |

|--------------------|----------------------------------|---------|---------------------------------------------------------------------------------------------------|

| 1                  | 7                                | OUT1    | Output of Channel 1; Short-circuit protected; integrated freewheeling diodes for inductive loads. |

| 2                  | 8                                | EF      | Error Flag; TTL/CMOS compatible output for error detection; (open drain)                          |

| 3                  | 9                                | IN1     | Control Input 1; TTL/CMOS compatible                                                              |

| 4                  | 1, 10,<br>11, 20                 | GND     | Ground; internally connected to tab                                                               |

| 5                  | 12                               | IN2     | Control Input 2; TTL/CMOS compatible                                                              |

| 6                  | 6, 15                            | $V_{S}$ | Supply Voltage; block to GND                                                                      |

| 7                  | 14                               | OUT2    | Output of Channel 2; Short-circuit protected; integrated freewheeling diodes for inductive loads. |

| _                  | 2, 3, 4, 5,<br>16, 17, 18,<br>19 | N.C.    | Not Connected                                                                                     |

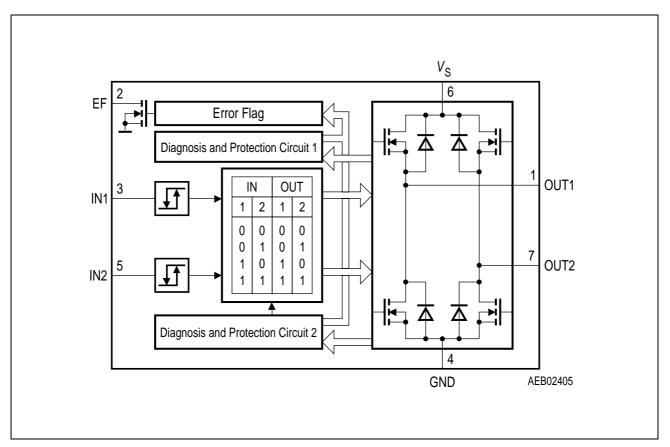

# 1.4 Functional Block Diagram

Figure 2 Block Diagram

# 1.5 Circuit Description

#### **Input Circuit**

The control inputs consist of TTL/CMOS-compatible schmitt-triggers with hysteresis. Buffer amplifiers are driven by this stages.

#### **Output Stages**

The output stages consist of a DMOS H-bridge. Integrated circuits protect the outputs against short-circuit to ground and to the supply voltage. Positive and negative voltage spikes, which occur when switching inductive loads, are limited by integrated freewheeling diodes.

A monitoring circuit for each output transistor detects whether the particular transitor is active and in this case prevents the corresponding source transistor (sink transistor) from conducting in sink operation (source operation). Therefore no crossover currents can occur.

#### 1.6 Input Logic Truth Table

#### **Functional Truth Table**

| IN1 | IN2 | OUT1 | OUT2 | Comments                                    |

|-----|-----|------|------|---------------------------------------------|

| L   | L   | L    | L    | Brake; both low side transistors turned-ON  |

| L   | Н   | L    | Н    | Motor turns counterclockwise                |

| Н   | L   | Н    | L    | Motor turns clockwise                       |

| Н   | Н   | Н    | Н    | Brake; both high side transistors turned-ON |

#### **Notes for Output Stage**

| Symbol | Value                                                               |

|--------|---------------------------------------------------------------------|

| L      | Low side transistor is turned-ON High side transistor is turned-OFF |

| Н      | High side transistor is turned-ON Low side transistor is turned-OFF |

# 1.7 Monitoring Functions

Undervoltage lockout (UVLO):

When  $V_{\rm S}$  reaches the switch on voltage  $V_{\rm S\,ON}$  the IC becomes active with a hysteresis. All output transistors are switched off if the supply voltage  $V_{\rm S\,OFF}$  drops below the switch off value  $V_{\rm S\,OFF}$ .

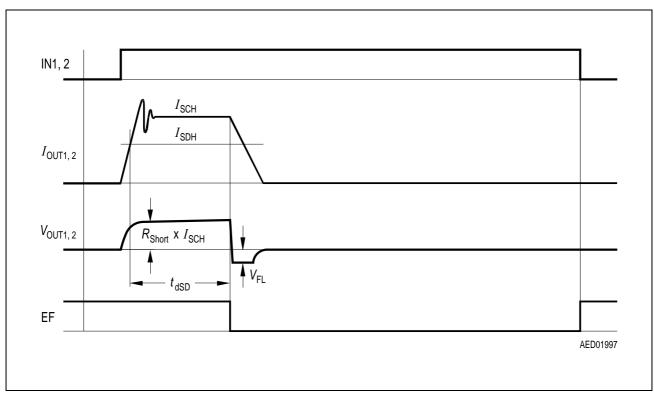

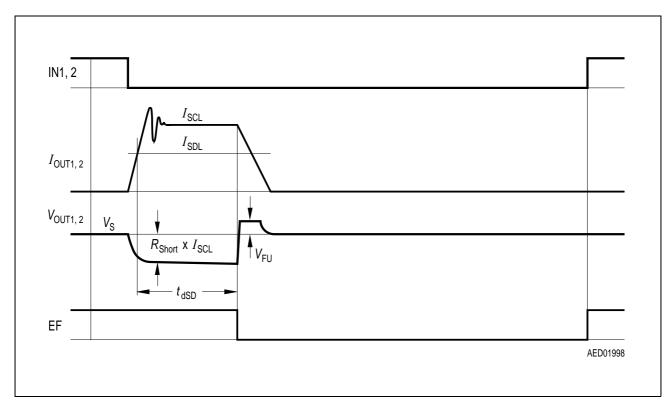

#### 1.8 Protective Function

Various errors like short-circuit to +  $V_{\rm S}$ , ground or across the load are detected. All faults result in turn-OFF of the output stages after a delay of 50  $\mu$ s and setting of the error flag EF to ground. Changing the inputs resets the error flag.

# a. Output Shorted to Ground Detection

If a high side transistor is switched on and its output is shorted to ground, the output current is internally limited. After a delay of 50  $\mu$ s all outputs will be switched-OFF and the error flag is set.

#### b. Output Shorted to + $V_{\rm S}$ Detection

If a low side transistor is switched on and its output is shorted to the supply voltage, the output current is internally limited. After a delay of 50  $\mu$ s all outputs will be switched-OFF and the error flag is set.

#### c. Overload Detection

An internal circuit detects if the current through the low side transistor exceeds the trippoint  $I_{SDL}$ . In this case all outputs are turned off after 50  $\mu$ s and the error flag is set.

#### d. Overtemperature Protection

At a junction temperature higher than 150 °C the thermal shutdown turns-OFF, all four output stages commonly and the error flag is set with a delay.

#### **Diagnosis**

## 2 Diagnosis

Various errors as listed in the table "Diagnosis" are detected. Short circuits and overload result in turning off the output stages after a delay  $t_{\rm dSD}$  and setting the error flag simultaneously [EF = L]. Changing the inputs to a state where the fault is not detectable resets the error flag (input toggling) with the exception of short circuit from OUT1 to OUT2 (load short circuit).

| Flag                                   | IN1 | IN2 | OUT1             | OUT2             | EF | Remarks        |

|----------------------------------------|-----|-----|------------------|------------------|----|----------------|

|                                        | 0   | 0   | L                | L                | 1  | Not detectable |

| Short circuit from OUT1 to OUT2        | 0   | 1   | X                | X                | 0  |                |

|                                        | 1   | 0   | X                | X                | 0  |                |

|                                        | 1   | 1   | Н                | Н                | 1  | Not detectable |

|                                        | 0   | 0   | GND              | L                | 1  | Not detectable |

| Short circuit from OUT1 to GND         | 0   | 1   | GND              | X                | 1  | Not detectable |

|                                        | 1   | 0   | GND              | L                | 0  |                |

|                                        | 1   | 1   | GND              | X                | 0  |                |

|                                        | 0   | 0   | L                | GND              | 1  | Not detectable |

| Short circuit from OUT2 to GND         | 0   | 1   | L                | GND              | 0  |                |

|                                        | 1   | 0   | X                | GND              | 1  | Not detectable |

|                                        | 1   | 1   | X                | GND              | 0  |                |

|                                        | 0   | 0   | $V_{	extsf{s}}$  | X                | 0  |                |

| Short circuit from OUT1 to $V_{\rm S}$ | 0   | 1   | $V_{\mathtt{s}}$ | Н                | 0  |                |

|                                        | 1   | 0   | $V_{	extsf{s}}$  | X                | 1  | Not detectable |

|                                        | 1   | 1   | $V_{	t s}$       | Н                | 1  | Not detectable |

|                                        | 0   | 0   | X                | $V_{\mathtt{s}}$ | 0  |                |

| Short circuit from OUT2 to $V_{\rm S}$ | 0   | 1   | X                | $V_{\mathtt{s}}$ | 1  | Not detectable |

|                                        | 1   | 0   | Н                | $V_{s}$          | 0  |                |

|                                        | 1   | 1   | Н                | $V_{	t s}$       | 1  | Not detectable |

| Overtemperature or undervoltage        | 0   | 0   | Z                | Z                | 0  |                |

|                                        | 0   | 1   | Z                | Z                | 0  |                |

|                                        | 1   | 0   | Z                | Z                | 0  |                |

|                                        | 1   | 1   | Z                | Z                | 0  |                |

IN: 0 = Logic LOW OUT: Z = Output in tristate condition EF: 1 = No error

1 = Logic HIGH L = Output in sink condition 0 = Error

H = Output in source conditionX = Voltage level undefined

For Open circuit detection, use the TLE 5205-2.

### 3 Electrical Characteristics

# 3.1 Absolute Maximum Ratings

$-40 \, ^{\circ}\text{C} < T_{\text{j}} < 150 \, ^{\circ}\text{C}$

| Parameter | Symbol | Limit Values |      | Unit | Remarks |

|-----------|--------|--------------|------|------|---------|

|           |        | min.         | max. |      |         |

# **Voltages**

| Supply voltage             | $V_{S}$                    | - 0.3      | 40 | V | _                                         |

|----------------------------|----------------------------|------------|----|---|-------------------------------------------|

|                            |                            | <b>– 1</b> | 40 | V | $t < 0.5 \text{ s}; I_{S} > -5 \text{ A}$ |

| Logic input voltage        | <i>V</i> <sub>IN1, 2</sub> | - 0.3      | 7  | V | 0 V < V <sub>S</sub> < 40 V               |

| Diagnostics output voltage | $V_{EF}$                   | - 0.3      | 7  | V | _                                         |

# **Currents of DMOS-Transistors and Freewheeling Diodes**

| Output current (cont.) | $I_{OUT1,2}$         | <b>-</b> 5 | 5 | Α | _                                                                         |

|------------------------|----------------------|------------|---|---|---------------------------------------------------------------------------|

| Output current (peak)  | I <sub>OUT1, 2</sub> | <b>-6</b>  | 6 | Α | $t_{\rm p}$ < 100 ms; $T$ = 1 s                                           |

| Output current (peak)  | I <sub>OUT1, 2</sub> | _          | _ | A | $t_{\rm p}$ < 50 $\mu$ s; $T$ = 1 s; internally limitted; see overcurrent |

# **Temperatures**

| Junction temperature | $T_{\rm j}$  | <b>- 40</b> | 150 | °C | _ |

|----------------------|--------------|-------------|-----|----|---|

| Storage temperature  | $T_{ m stg}$ | <b>-</b> 50 | 150 | °C | _ |

#### **Thermal Resistances**

| Junction case    | $R_{thjC}$ | _ | 3  | K/W | P-TO220-7-11/12,<br>P-TO263-7-1 |

|------------------|------------|---|----|-----|---------------------------------|

| Junction ambient | $R_{thjA}$ | _ | 65 | K/W | P-TO220-7-11/12                 |

|                  |            | _ | 75 | K/W | P-TO263-7-1                     |

| Junction case    | $R_{thjC}$ | - | 5  | K/W | P-DSO-20-12                     |

| Junction ambient | $R_{thjA}$ | _ | 50 | K/W | P-DSO-20-12                     |

Note: Maximum ratings are absolute ratings; exceeding any one of these values may cause irreversible damage to the integrated circuit.

# 3.2 Operating Range

| Parameter                 | arameter Symbol Limit Values |            | Unit        | Remarks |                                                |

|---------------------------|------------------------------|------------|-------------|---------|------------------------------------------------|

|                           |                              | min.       | max.        |         |                                                |

| Supply voltage            | $V_{S}$                      | $V_{UVON}$ | 40          | V       | After $V_{\rm S}$ rising above $V_{\rm UV~ON}$ |

| Supply voltage increasing |                              | - 0.3      | $V_{UVON}$  | V       | Outputs in tristate                            |

| Supply voltage decreasing |                              | - 0.3      | $V_{UVOFF}$ | V       | condition                                      |

| Logic input voltage       | V <sub>IN1, 2</sub>          | - 0.3      | 7           | V       | _                                              |

| Junction temperature      | $T_{j}$                      | - 40       | 150         | °C      | _                                              |

#### 3.3 Electrical Characteristics

6 V <  $V_{\rm S}$  < 18 V; IN1 = IN2 = HIGH

$I_{\rm OUT1, \, 2} = 0$  A (No load);  $-40 \, ^{\circ}{\rm C} < T_{\rm j} < 150 \, ^{\circ}{\rm C}$ ; unless otherwise specified

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

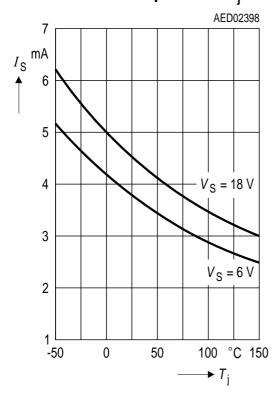

# **Current Consumption**

| Quiescent current | $I_{S}$ | _ | _ | 10 | mA | IN1 = IN2 = LOW;     |

|-------------------|---------|---|---|----|----|----------------------|

|                   |         |   |   |    |    | $V_{\rm S}$ = 13.2 V |

# **Under Voltage Lockout**

| UV-Switch-ON voltage  | $V_{UVON}$  | _   | 5.3 | 6   | V | $V_{ m S}$ increasing      |

|-----------------------|-------------|-----|-----|-----|---|----------------------------|

| UV-Switch-OFF voltage | $V_{UVOFF}$ | 3.5 | 4.7 | 5.6 | V | $V_{ m S}$ decreasing      |

| UV-ON/OFF-Hysteresis  | $V_{UVHY}$  | 0.2 | 0.6 | _   | V | $V_{ m UVON}-V_{ m UVOFF}$ |

#### **Electrical Characteristics** (cont'd) 3.3

6 V <  $V_{\rm S}$  < 18 V; IN1 = IN2 = HIGH  $I_{\rm OUT1,~2}$  = 0 A (No load); – 40 °C <  $T_{\rm j}$  < 150 °C; unless otherwise specified

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

# Outputs OUT1, 2

#### **Static Drain-Source-On Resistance**

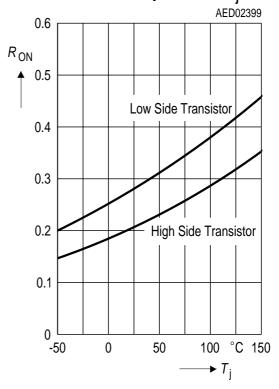

| Source $I_{\text{OUT}} = -3 \text{ A}$ | $R_{DSONH}$ | _ | 220 | 350  | mΩ | $6 \text{ V} < V_{\text{S}} < 18 \text{ V}$<br>$T_{\text{j}} = 25 \text{ °C}$      |

|----------------------------------------|-------------|---|-----|------|----|------------------------------------------------------------------------------------|

|                                        |             |   | _   | 500  | mΩ | 6 V < V <sub>S</sub> < 18 V                                                        |

|                                        |             |   | 350 | 500  | mΩ | $V_{\text{S ON}} < V_{\text{S}} \le 6 \text{ V}$<br>$T_{\text{j}} = 25 \text{ °C}$ |

|                                        |             |   | _   | 800  | mΩ | $V_{\rm S~ON} < V_{\rm S} \le 6~{\rm V}$                                           |

| Sink $I_{\text{OUT}} = 3 \text{ A}$    | $R_{DSONL}$ | _ | 230 | 350  | mΩ | $6 \text{ V} < V_{\text{S}} < 18 \text{ V}$<br>$T_{\text{j}} = 25 \text{ °C}$      |

|                                        |             |   | _   | 500  | mΩ | 6 V < V <sub>S</sub> < 18 V                                                        |

|                                        |             |   | 400 | 600  | mΩ | $V_{\text{S ON}} < V_{\text{S}} \le 6 \text{ V}$<br>$T_{\text{j}} = 25 \text{ °C}$ |

|                                        |             |   | _   | 1000 | mΩ | $V_{\rm S~ON} < V_{\rm S} \le 6~{ m V}$                                            |

Note: Values of  $R_{DS \ ON}$  for  $V_{S \ ON} < V_S \le 6$  V are guaranteed by design.

#### **Overcurrent**

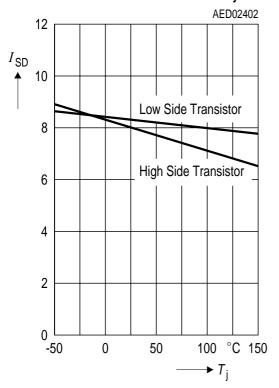

| Source shutdown trippoint | $-I_{SDH}$    | _  | _  | 10 | Α  | $T_{\rm j}$ = $-$ 40 °C        |

|---------------------------|---------------|----|----|----|----|--------------------------------|

|                           |               | _  | 8  | _  | Α  | $T_{\rm j}$ = 25 °C            |

|                           |               | 6  | _  | _  | Α  | <i>T</i> <sub>j</sub> = 150 °C |

| Sink shutdown trippoint   | $I_{SDL}$     | _  | _  | 10 | Α  | $T_{\rm j}$ = $-$ 40 °C        |

|                           |               | _  | 8  | _  | Α  | $T_{\rm j}$ = 25 °C            |

|                           |               | 6  | _  | _  | Α  | <i>T</i> <sub>j</sub> = 150 °C |

| Shutdown delay time       | $t_{\sf dSD}$ | 25 | 50 | 80 | μs | _                              |

# 3.3 Electrical Characteristics (cont'd)

6 V <  $V_{\rm S}$  < 18 V; IN1 = IN2 = HIGH

$I_{\rm OUT1,\,2} = 0$  A (No load);  $-40~{\rm ^{\circ}C} < T_{\rm j} < 150~{\rm ^{\circ}C}$ ; unless otherwise specified

| Parameter | Symbol | Lir  | nit Valu | ies  | Unit | Test Condition |

|-----------|--------|------|----------|------|------|----------------|

|           |        | min. | typ.     | max. |      |                |

#### **Short Circuit Current Limitation**

| Source current | $-I_{SCH}$ | _ | _ | 20 | А | $t < t_{\sf dSD}$ |

|----------------|------------|---|---|----|---|-------------------|

| Sink current   | $I_{SCL}$  | _ | _ | 15 | Α | $t < t_{\sf dSD}$ |

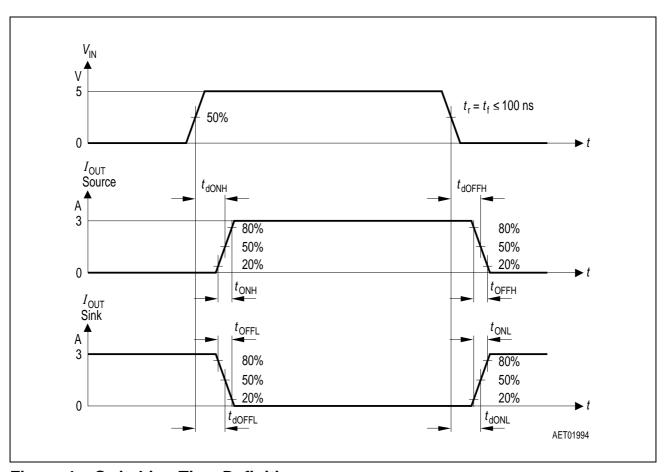

# Output Delay Times (Device Active for t > 1 ms)

| Source ON  | t <sub>d ON H</sub>  | _ | 10 | 20 | μs | $I_{\text{OUT}} = -3 \text{ A}$ resistive load |

|------------|----------------------|---|----|----|----|------------------------------------------------|

| Sink ON    | t <sub>d ON L</sub>  | _ | 10 | 20 | μs | I <sub>OUT</sub> = 3 A resistive load          |

| Source OFF | t <sub>d OFF H</sub> | _ | 2  | 5  | μs | $I_{\text{OUT}} = -3 \text{ A}$ resistive load |

| Sink OFF   | t <sub>d OFF L</sub> | _ | 2  | 5  | μs | I <sub>OUT</sub> = 3 A resistive load          |

# Output Switching Times (Device Active for t > 1 ms)

| Source ON  | t <sub>ON H</sub>  | _ | 15 | 30 | μs | $I_{\text{OUT}} = -3 \text{ A}$ resistive load |

|------------|--------------------|---|----|----|----|------------------------------------------------|

| Sink ON    | t <sub>ON L</sub>  | _ | 5  | 10 | μs | $I_{\text{OUT}} = 3 \text{ A}$ resistive load  |

| Source OFF | t <sub>OFF H</sub> | _ | 2  | 5  | μs | $I_{\text{OUT}} = -3 \text{ A}$ resistive load |

| Sink OFF   | t <sub>OFF L</sub> | _ | 2  | 5  | μs | I <sub>OUT</sub> = 3 A resistive load          |

# **Clamp Diodes**

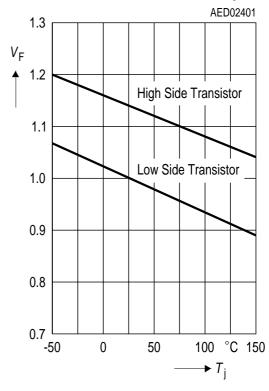

# **Forward Voltage**

| High-side | $V_{FH}$ | _ | 1   | 1.5 | V | <i>I</i> <sub>F</sub> = 3 A |

|-----------|----------|---|-----|-----|---|-----------------------------|

| Low-side  | $V_{FL}$ | _ | 1.1 | 1.5 | ٧ | <i>I</i> <sub>F</sub> = 3 A |

# 3.3 Electrical Characteristics (cont'd)

6 V <  $V_{\rm S}$  < 18 V; IN1 = IN2 = HIGH

$I_{\rm OUT1,\,2} = 0$  A (No load);  $-40~{\rm ^{\circ}C} < T_{\rm j} < 150~{\rm ^{\circ}C}$ ; unless otherwise specified

| Parameter | Symbol | Lir  | nit Valu | ies  | Unit | Test Condition |

|-----------|--------|------|----------|------|------|----------------|

|           |        | min. | typ.     | max. |      |                |

# **Leakage Current**

| Source | $I_{LKH}$ | - 100 | - 35 | _   | μΑ | OUT1 = $V_{\rm S}$ |

|--------|-----------|-------|------|-----|----|--------------------|

| Sink   | $I_{LKL}$ | _     | 35   | 100 | μΑ | OUT2 = GND         |

# Logic

# **Control Inputs IN 1, 2**

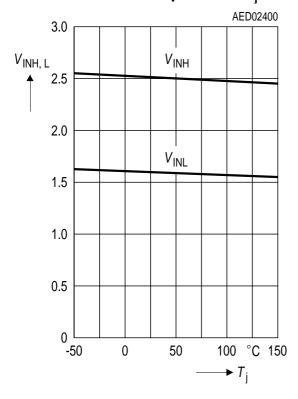

| H-input voltage threshold   | $V_{INH}$  | 2.8  | 2.5 | _   | V  | _                 |

|-----------------------------|------------|------|-----|-----|----|-------------------|

| L-input voltage             | $V_{INL}$  | _    | 1.7 | 1.2 | V  | _                 |

| Hysteresis of input voltage | $V_{INHY}$ | 0.4  | 0.8 | 1.2 | V  | _                 |

| H-input current             | $I_{INH}$  | -2   | _   | 2   | μΑ | $V_{IN}$ = 5 V    |

| L-input current             | $I_{INL}$  | - 10 | - 4 | 0   | μΑ | $V_{IN} = 0 \; V$ |

# **Error Flag Output EF**

| Low output voltage | $V_{EFL}$ | _ | 0.25 | 0.5 | V  | $I_{EF} = 3 \; mA$ |

|--------------------|-----------|---|------|-----|----|--------------------|

| Leakage current    | $I_{EFL}$ | _ | _    | 10  | μΑ | $V_{EF}$ = 7 V     |

#### **Thermal Shutdown**

| Thermal shutdown junction temperature  | $T_{jSD}$  | 150 | 175 | 200 | °C | _ |

|----------------------------------------|------------|-----|-----|-----|----|---|

| Thermal switch-on junction temperature | $T_{jSO}$  | 120 | _   | 170 | °C | _ |

| Temperature hysteresis                 | $\Delta T$ | _   | 30  | _   | K  | _ |

Note: Values of thermal shutdown are guaranteed by design.

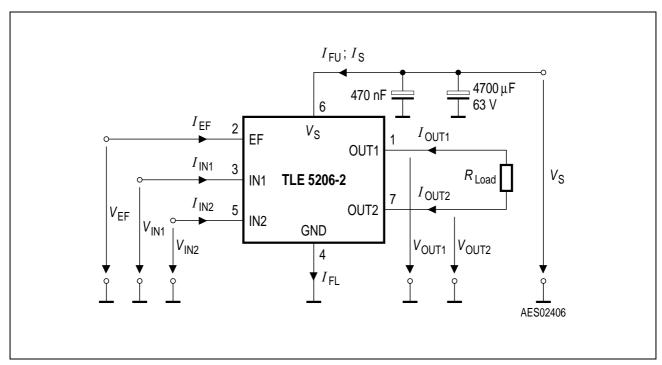

Figure 3 Test Circuit

|           | Overcurrent | Short Circuit | Open Circuit |

|-----------|-------------|---------------|--------------|

| $I_{OUT}$ | $I_{SD}$    | $I_{SC}$      | $I_{OC}$     |

Figure 4 Switching Time Definitions

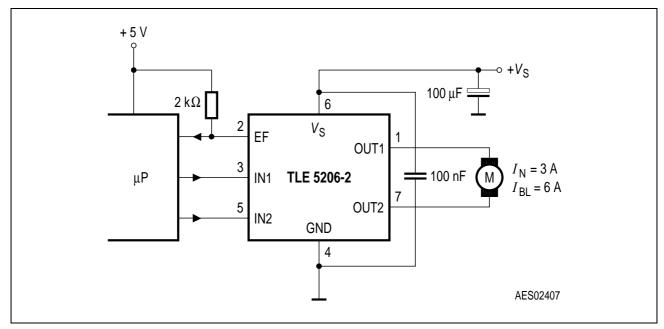

Figure 5 Application Circuit

#### **Application Modes**

## 1. Simple CW/CCW-Control

For low-cost application simple CW/CCW-Control without any speed regulation is recommended. A low-speed two-line interface is sufficient for the brake low, clockwise, counter clockwise and brake high command.

#### 2. Sign/Magnitude Control

For this mode two ports with PWM capability are necessary. Motor turns clockwise (current flows from OUT1 to OUT2; means: OUT1 is switched HIGH continuously and OUT2 is PWM controlled.

To achieve motor counter clockwise turning change input signals to: IN1 = PWM; IN2 = H.

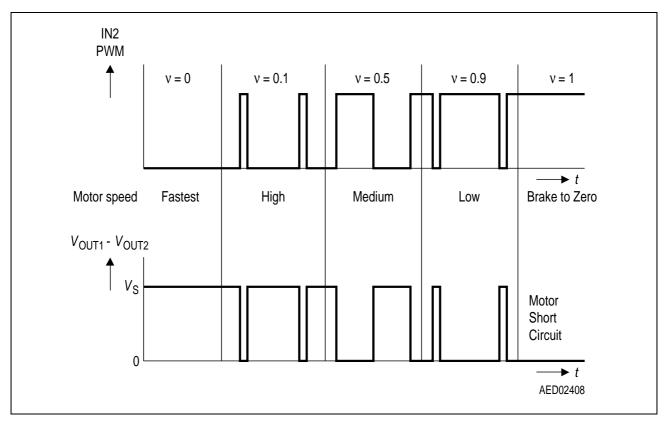

Figure 6 Input/Output Diagram for CW Operation (IN1 = H)

#### 3. Locked Anti-Phase Control

The most important advantage to drive a motor in locked anti-phase mode is: Only one variable duty cycle signal is necessary in which is encoded both direction- and amplitude information. So the interface is very simple: A PWM input driven by a dedicated PWM port from  $\mu P$ .

Figure 7 Timing Diagram for Output Shorted to Ground

Figure 8 Timing Diagram for Output Shorted to  $V_{\mathrm{S}}$

# Diagrams Quiescent Current $I_{\rm S}$ (active) versus Junction Temperature $T_{\rm i}$

# Input Switching Thresholds $V_{\mathrm{INH,\,L}}$ versus Junction Temperature $T_{\mathrm{i}}$

# Static Drain-Source ON-Resistance versus Junction Temperature $T_{\rm i}$

# Clamp Diode Forward Voltage $V_{\mathsf{F}}$ versus Junction Temperature $T_{\mathsf{j}}$

# Overcurrent Shutdown Threshold $I_{\rm SD}$ versus Junction Temperature $T_{\rm i}$

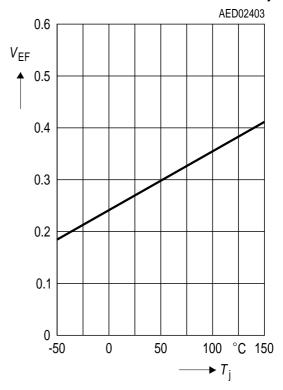

# Error-Flag Saturation Output Voltage $V_{\rm EF}$ versus Junction Temperature $T_{\rm j}$

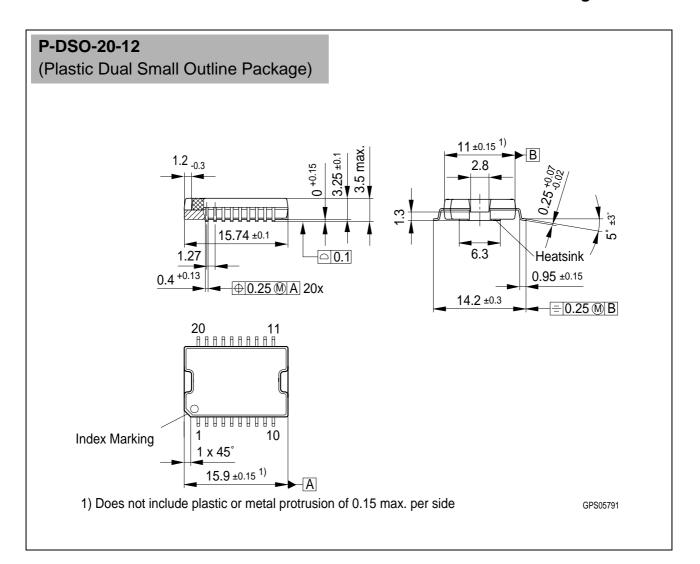

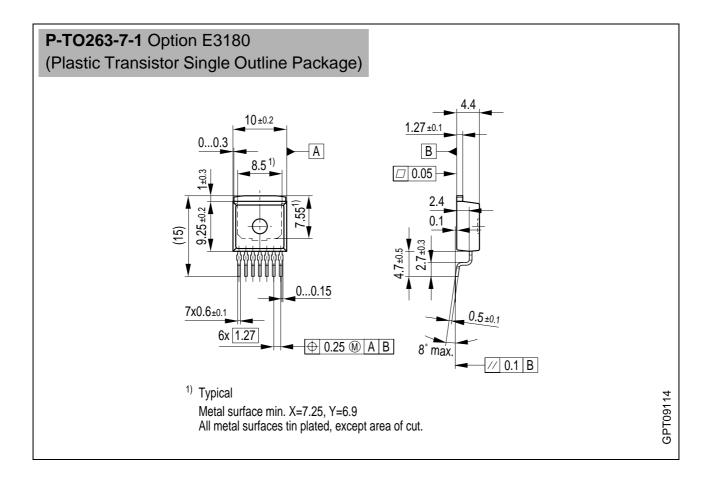

# 4 Package Outlines

#### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

#### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device

#### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device

# P-TO220-7-12 (Plastic Transistor Single Outline Package) $10 \pm 0.2$ 9.9±0.2 8.5<sup>1)</sup> $1.27 \pm 0.1$ 0...0.3 12.95<sup>1)</sup> 15.65±0.3 □ 0.05 2.4 Ċ $0.5 \pm 0.1$ 0...0.15 2.4 $7x \, 0.6 \pm 0.1$ 6x 1.27 ⊕ 0.25 M A B C 1) Typical Metal surface min. X=7.25, Y=12.3 All metal surfaces tin plated, except area of cut.

# Sorts of Packing

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".